rev. 1.6

## Introducción

El presente documento resume los aspectos más importantes de la Revision B.3 de la especificación WISHBONE.

El objetivo de la especificación Wishbone es crear una interfaz común entre IP Cores.

Define una forma estándar de *intercambiar datos* entre módulos IP Core. No pretende especificar el funcionamiento del core, solo la forma de comunicarse con él.

La arquitectura WISHBONE es análoga al bus de un microprocesador.

- o ofrece una solución flexible de integración

- o ofrece varios tipos de ciclos y anchos de bus para resolver distintas situaciones.

- o permite que una misma aplicación sea desarrollada por varios fabricantes.

### Características

Las características más sobresalientes de la especificación son:

- o Basado en protocolos estándares de transferencia de datos

- ciclos READ/WRITE

- o ciclos de transferencia en BLOQUE

- o ciclos RMW.

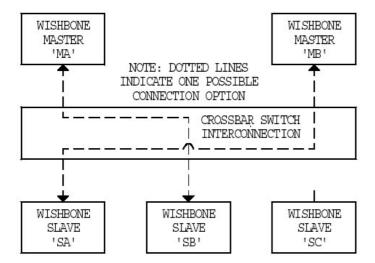

- o Soporta varios tipos de interconexionamientos

- o punto a punto

- bus compartido

- o switch de interconexiones.

- o Protocolo de Handshake para regular la velocidad de transferencia de datos.

- Soporta varias terminaciones de ciclos

- o normal

- con retry

- por error

- o Basado en arquitectura Maestro/Esclavo

## Terminología

La especificación WISHBONE define los siguientes términos.

### Regla

Todas **DEBEN** ser seguidas para asegurar una compatibilidad entre interfaces.

#### Recomendaciones

Cuando aparece una recomendación, **SE ACONSEJA** seguirla. El no adoptarla puede implicar una perdida de performance.

Muchas recomendaciones están basadas en la experiencia acumulada de los diseñadores que escribieron la especificación.

### Sugerencia

Es **UN CONSEJO** que puede ser considerado por el diseñador. Puede ser útil, pero no vital para el funcionamiento de la interfaz.

#### Permiso

Cuando se indica que algo **PUEDE** hacerse o no, la decisión de implementarlo puede quedar a cargo del diseñador.

#### Observación

Usualmente son textos que clarifican alguna situación, pero no aportan nada más que eso.

## Convención para el nombre de la señales

Todas las señales tiene "\_I" y "\_O" para indicar si son salidas o entradas al Core.

Los buses son indicados por nombres seguidos de (). Por ejemplo DAT\_I().

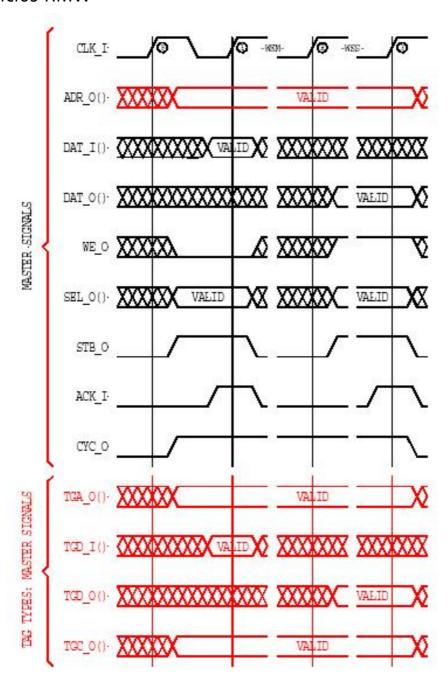

Pueden utilizarse señales especiales definidas por el usuario, por ejemplo PAR\_O. Estas señales son llamadas *tags*. Los tags tiene asociados un *TAG TYPE* que indican en que momento del ciclo tienen un valor valido.

# Especificación de la Interfaz

### Documentación de la interfaz

Al especificar la interfaz, debe de incluirse la siguiente información.

- 1. N° de revisión WISHBONE con la cual es compatible el Core. Pare este caso **B.3**

- 2. Tipo de Interfaz: Maestro o Esclavo

- 3. El nombre de las señales definidas en la interfaz WB.

- 4. En caso de soportar señalización de Errores

- o Master (ERR\_I) debe indicar como reacciona.

- Slave (ERR\_O) debe indicar cuales son las condiciones que activan la señal.

- 5. En caso de soportar señalización Retry

- Master (RTY\_I) debe indicar como reacciona.

- Slave (RTY O) debe indicar cuales son las condiciones que activan la señal.

- 6. Todas las interfaces que soportan TAGS, deben indicar su nombre, el tipo y su funcionamiento

- 7. Ancho del bus de datos (8, 16, 32, 64)

- 8. Granularidad del puerto.

- 9. Tamaño máximo del operando, en caso de no conocerse, es igual al ancho de bus.

- 10.BIG ENDIAN o LITTLE ENDIAN

- 11.Si hay restricciones sobre la señal CLK\_I.

### Niveles activos

Todas las señales son activas por nivel alto.

## Señales en la interfaz

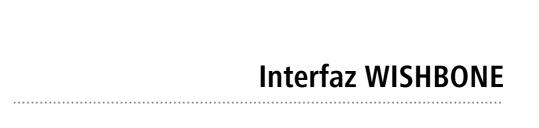

La idea es que las señales permitan las conexiones punto a puto, bus compartido, etc.

Permiten tres ciclos básicos: Read, Write y RMW. Pero no hay obligación de soportarlos a todos.

Permiten un Handshake para adecuar la velocidad de transferencia de datos, e indicar errores y retry.

Las señales no son Bidireccionales, siempre son entradas o salidas. Esto es así pues muchas veces el diseño puede llagar a querer implementarse en hardware que no soporta internamente señales bidireccioneles, por ejemplo los FPGAs de Altera.

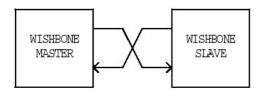

Ejemplo de interfaz e interconecciones en una arquitectura punto a punto:

### Comunes a Master y Slave

- o CLK\_I: entrada de reloj

- o RST I: reset del diseño

- o DAT\_I() y DAT\_O(): buses de entrada y salida de datos

- o TGD\_I() y TGD\_O()

- Opcional

- o Lleva información asociada al bus de datos

- Validas cuando STB\_O activo

- ∘ Ej: paridad

#### Master

- ADR O(N..n)

- N: Limite superior dado por el ancho del bus de direcciones

- on: limite inferior dado por la granularidad del bus de datos.

- CYC\_O: Indica que se esta llevando a cabo un ciclo de bus válido. Se activa al comienzo del ciclo y permanece hasta el final.

- WE\_O: Indica si el ciclo es de lectura o escritura.

- o STB\_O: indica que se esta llevando a cabo un ciclo valido de transferencia de datos.

- o ACK\_I: recibe la confirmación de una transferencia.

- ERR 1: recibe la indicación de un error en la transferencia.

- o RTY\_I: recibe pedido de re-transmisión de datos.

- rev. 1.6

- LOCK\_O: indica que el ciclo que se esta llevando a cabo no puede ser interrumpido.

- SEL\_O(): asociado con la granularidad, indica donde hay o donde espera datos validos en el bus.

- TGA\_O

- o Información asociada a las lineas de direcciones

- Validas cuando STB O activo

- o TGC\_O

- o Información asociada con el tipo de ciclo de bus

- Validas cuando CYC\_O activo

### Slave

- o ADR I(N..n):

- N: Limite superior dado por el ancho del bus de direcciones

- o n: limite inferior dado por la granuralidad del bus de datos.

- o CYC\_I: indica el comienzo de un ciclo.

- o WE\_I: indica si la transacción es de lectura o escritura.

- o STB\_I: indica que se esta llevando a cabo un ciclo valido de transferencia de datos.

- o ACK\_O: indica que la transferencia se ha realizado en forma exitosa.

- o ERR\_O: utilizado para señalizar un error en la transacción.

- o RTY\_O: utilizado para pedir una reintento en la transacción.

- o LOCK\_I: indica que el ciclo que se esta llevando a cabo no puede ser interrumpido

- SEL\_I(): asociado con la granularidad, indica donde hay o donde espera datos validos en el bus.

- o TGA I

- o Información asociada a las lineas de direcciones

- Validas cuando STB I activo

- o TGC I

- o Información asociada con el tipo de ciclo de bus

- Validas cuando CYC\_I activo

## WISHBONE clásico

A partir de la revisión B.3, se agregó una nueva modalidad de transacciones y se agregaron TAGs de señalización.

Los cambios permiten una mayor velocidad en la transferencia de datos, pero se mantiene la compatibilidad con las revisiones anteriores del estándar Wishbone.

A la manera de realizar transacciones de las versiones anteriores se les llama "Wishbone clásico"

## Funcionamiento general

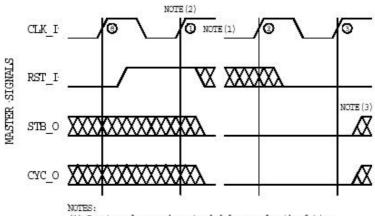

#### Reset

EL reset se produce en forma síncrona.

- Reset cycles can be extended for any length of time. Self-starting state machines & counters reset themselves at the rising [CLK\_I] edge following the assertion of [RST\_I].

On MASTERS, [STB 0] and [CYC 0] are negated at the same time.

On MASTERS, [STB 0] and [CYC 0] may be asserted at the rising [CLK\_I] edge following the negation of [RST\_I].

Todas las interfaces WISHBONE deben de inicializarse con el primer flanco de subida en el que RST\_I este activo.

#### Inicialización de ciclo de transacción.

Se indica que hay un ciclo válido si CYC\_O esta activo. Cuando CYC\_O es 0 ninguna de las otras señales del MASTER tienen sentido.

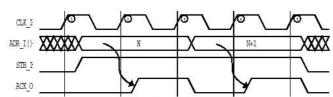

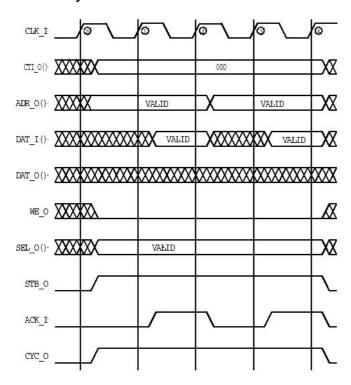

### Protocolo de Handshake

El hanshake para la transferencia de datos es sumamente sencillo, el MASTER activa STB\_O y lo mantiene así hasta que el esclavo activa alguna de las señales ACK\_I, ERR\_I, RTY\_I. Al ocurrir esto el Maestro desactiva la señal.

Las señales de respuesta ACK\_O, ERR\_O, RTY\_O deben generarse solo si están activas CYC\_I y STB\_I.

Las interfaces del esclavo **DEBEN** de ser diseñadas para que ACK\_O, ERR\_O, RTY\_O se activen y desactiven respondiendo a STB\_O.

### Uso de TAGS

| Descripción     | TAG TYPE  | Asociado a |

|-----------------|-----------|------------|

| Address tag     | TGA_I/O() | ADR_I/O()  |

| Data tag,input  | TGD_I()   | DAT_I()    |

| Data tag,output | TGD_O()   | DAT_O()    |

| Cycle tag       | TGC_O()   | Bus Cycle  |

Ejemplo de definición para señal PAR\_O

SIGNAL NAME: PAR\_O

DESCRIPTION: Even parity bitMASTER TAG TYPE: TGD\_O()

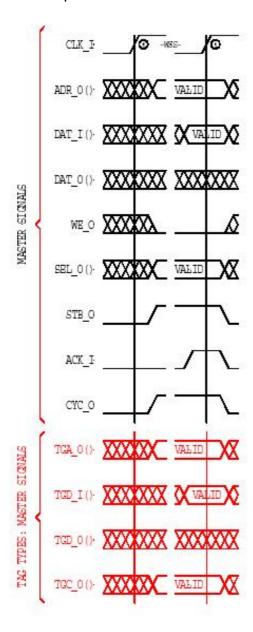

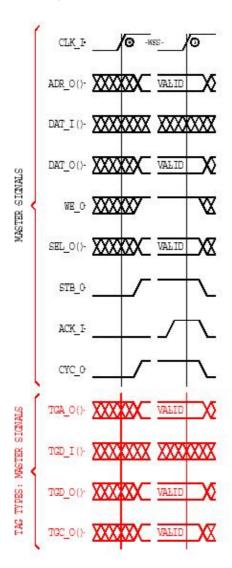

# Ciclos READ/WRITE Simple

# Read simple

# Write simple

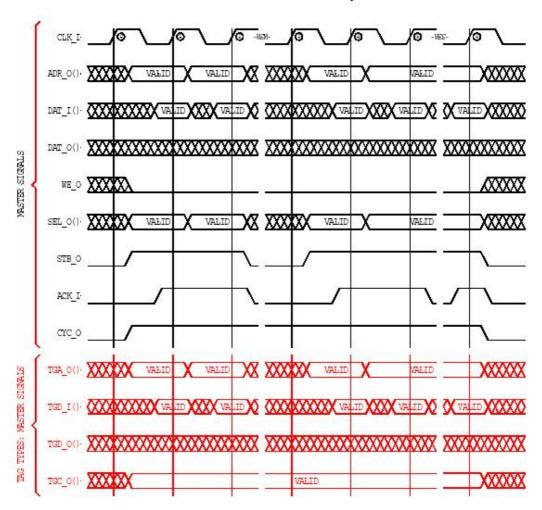

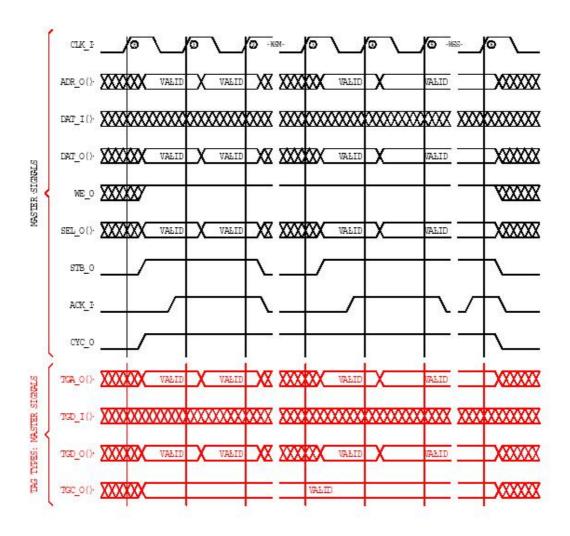

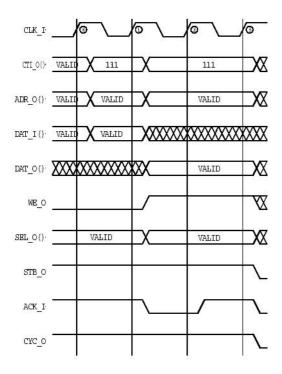

## Ciclos READ/WRITE en bloque

Durante las transferencias en bloque, la interfaz básicamente realiza transferencias simples Read/Write.

Este tipo de transferencias es útil, sobre todo en sistemas con varios Master.

## Read en Bloque

Puede realizarse una transferencia en cada ciclo de reloj.

## Write en Bloque

Puede realizarse una transferencia en cada ciclo de reloj.

# Ciclos RMW

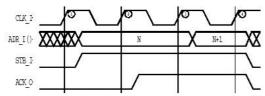

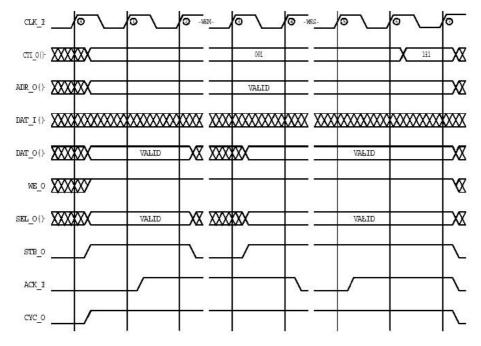

# WISHBONE con Ciclos de bus registrados.

Para lograr la máxima tasa de transferencia, WISHBONE necesita que las señales de terminación de ciclos (ACK\_I, ERR\_I,RTY\_I) sean generadas en forma asíncrona. Por ejemplo ACK\_O como el AND de CYC\_I y STB\_I.

Pero esto puede llevar a tener retardos demasiado grandes en el chip, dado que una señal pasa por varias compuertas.

La solución para esto es registrar las señales de terminación de ciclos.

Figure 4-3 WISHBONE Classic synchronous cycle terminated burst

El problema de esto es que genera un WAIT STATE, reduciendo a la mitad la taza de transferencia.

Esto se soluciona con TAGS que identifican el tipo de ciclo que se esta llevando a cabo. Se puede indicar si la transferencia actual es la última o si se siguen transfiriendo datos aún. Con esto se sabe si se debe desactivar ACK\_O o mantener activo en el siguiente período de reloj.

Figure 4-4 Advanced synchronous terminated burst

La interfaces que funcionan como WISHBONE con ciclos registrados, también soportan WB clásico.

## TAGS utilizados

### CTI\_IO()

- Cycle Type Identifier CTI\_O() del tipo TGC\_O() y CTI\_I() del tipo TGC\_I()

- El MASTER es el que envía la información. El ESCLAVO puede utilizarlo para preparar su respuesta.

- Para aprovechar al máximo el ancho de banda , tanto la interfaz Master como esclava deben de soportar el modo de trabajo.

| CTI_O(2:0) | Descripción                  |

|------------|------------------------------|

| 000        | Classic cycle.               |

| 001        | Constant address burst cycle |

| 010        | Incrementing burst cycle     |

| 011        | Reserved                     |

| 100        | Reserved                     |

| 101        | Reserved                     |

| 110        | Reserved                     |

| 111        | End-of-Burst                 |

|            |                              |

Las interfaces que soportan Ciclos Registrados, deben soportar al menos el modo clásico, para asegurar compatibilidad.

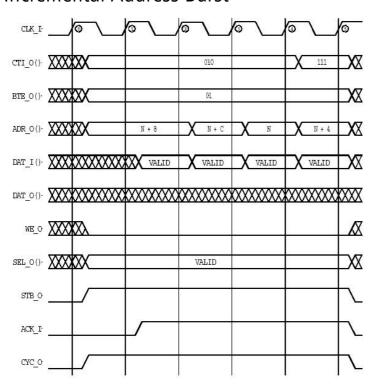

### BTE IO()

- Burst Type Extension BTE\_O() y BTE\_I() del Tipo TGA\_N()

- o Dan información adicional de como se incrementan las direcciones.

| BTE_IO(1:0) | Descripción        |

|-------------|--------------------|

| 00          | Linear burst       |

| 01          | 4-beat wrap burst  |

| 10          | 8-beat wrap burst  |

| 11          | 16-beat wrap burst |

Las interfaces que soportan BURST incremental, deben de soportar BTE\_O() y BTE\_I().

# Classic Cycle

# **End Of Burst**

# Constant Address Cycle

# **Incremental Address Burst**

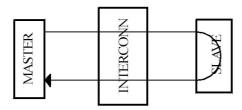

## Interconecciones de Módulos

WISHBONE facilita el trabajo a los diseñadores, ya que estandariza la interfaz.

Esta basado en una arquitectura de Maestro/Esclavo y se comunican a través de una interfaz usualmente denominada INTERCON.

INTERCON no es nada mágico, es también un archivo más escrito en un lenguaje de descripción de HW.

## Conexiones punto a punto

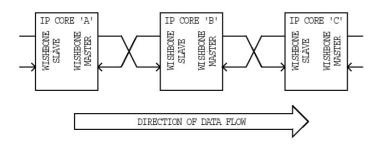

## Flujo de Datos

Es una posible arquitectura para implementar diseños que procesen datos en pipeline.

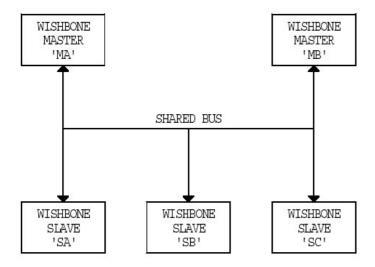

## Bus compartido

Todos los dispositivos están conectados sobre un mismo bus y cualquier Master puede iniciar un transacción con cualquier esclavo.

Un arbitro es el que determina cuando le toca el turno a cada uno de los Master.

## Switch de interconexiones

Consume más recursos, pero permite varia comunicaciones entre pares Maestro/Esclavo a la misma vez.