El bus PCI es el estándar actual para la conexión de tarjetas en un PC. Permite conectar placas que le agregan funcionalidades, por ejemplo placas de sonido, capturadoras de video, placas de red, co-procesadores matemáticos, etc. Estas tarjetas suelen llamarse placas PCI.

El diseño de prototipos de placas PCI, ya sea para su posterior uso comercial o para investigación, se ve acelerado si se comienza el desarrollo a partir de un placa de propósito general, ya existente, que pueda ser rápidamente adaptada según las necesidades del diseño.

Haciendo énfasis en la adaptabilidad de la placa a la aplicación a desarrollar, la electrónica que la conforme debe ser fácilmente modificable. Hoy día, este objetivo se logra utilizando circuitos integrados de lógica reconfigurable, como ser los FPGA.

Un FPGA puede verse como una caja llena de flip-flops, compuertas lógicas y memorias RAM, que pueden ser interconectados de una cierta manera, a gusto del usuario, al configurarlo.

Partiendo de una placa PCI cuyo corazón sea un FPGA, el diseño de un prototipo consistirá básicamente en realizar, en algún lenguaje de descripción de circuitos, un diseño que configure el FPGA para que se comporte según los requerimientos establecidos. Como un FPGA puede reconfigurarse, en caso de detectar un error en el funcionamiento, basta corregir el error y volver a configurar el FPGA.

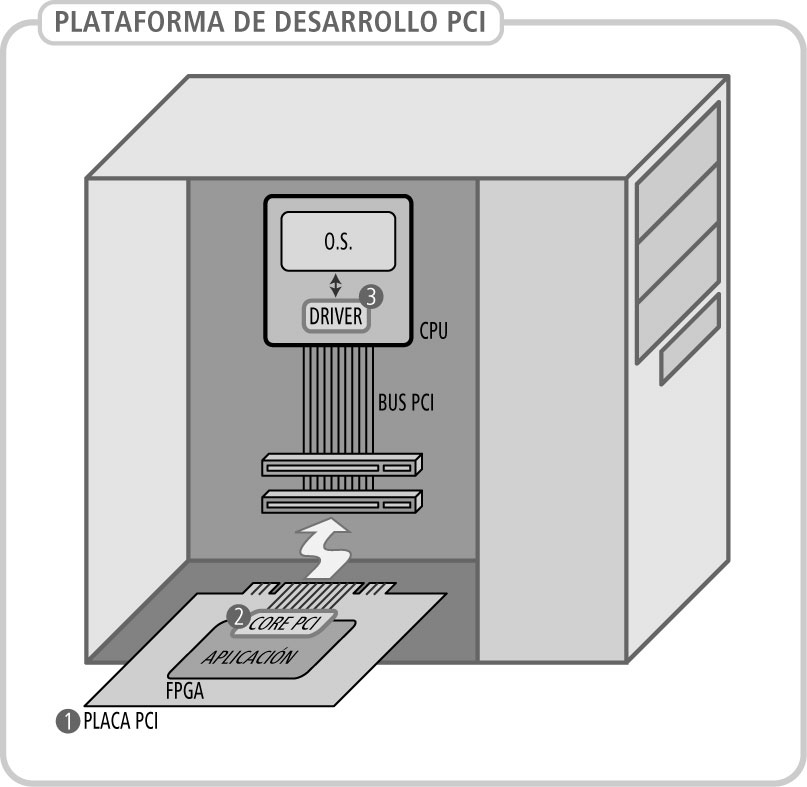

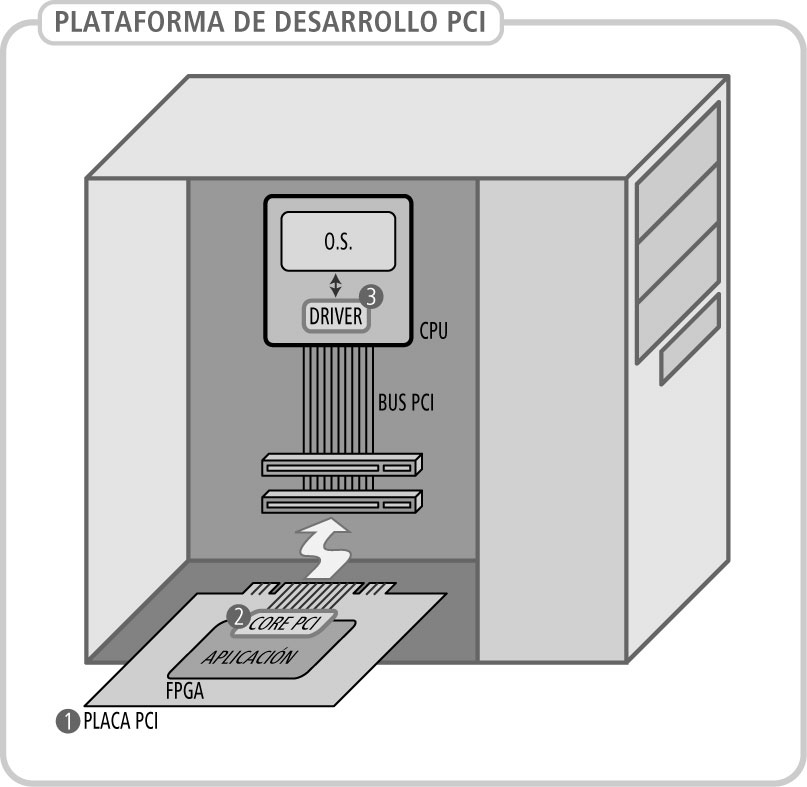

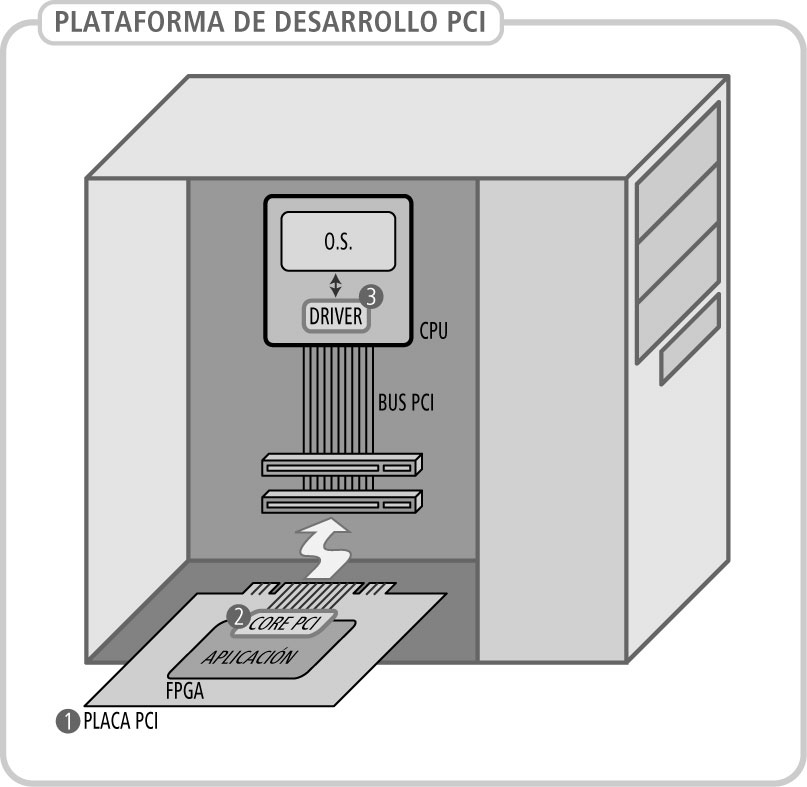

El diseño a programar en el FPGA debe implementar la funcionalidad que se desea agregar al PC y debe comunicarse utilizando el bus PCI.

Dada la complejidad del bus PCI, este diseño podría separarse en dos bloques, uno que resuelva la comunicación con el bus y otro que implemente la funcionalidad.

El bloque que resuelve la comunicación es llamado core PCI y se encarga de encapsular los detalles del estándar (manejo de errores, decodificación de direcciones, señalizaciones, etc.).

Inicialmente el proyecto planteaba el desarrollo de un core PCI de libre distribución y un software controlador genérico (driver) que permite al sistema operativo acceder a los recursos provistos por la placa PCI.

Las primeras versiones del core PCI fueron probadas en la placa PCI con lógica reconfigurable con la que cuenta el Instituto de Ingeniería Eléctrica (IIE). Estas primeras pruebas no cumplieron con los requerimientos de performance necesarios debido a que los FPGAs de la placa son lentos.

Por esta razón se incluyó como parte de los objetivos del proyecto, el diseño y fabricación de una placa PCI de bajo costo con lógica reconfigurable.

El resultado final del proyecto es una plataforma de desarrollo para diseños hardware que utilizan el bus PCI.

La plataforma esta compuesta por:

Características de la placa:

Características del core PCI:

Características del driver:

The PCI bus the current standard for the interconnection of PCI device cards installed in a PC. It defines an interface for connecting devices that add a certain function, for example, a sound, video capture, network access, mathematical co-processors, etc.

Prototyping a PCI device card for a commercial purpose or for research is greatly simplified by using an already designed and tested general purpose development card that can be easily adapted according to the requirements of the project.

As the PCI card must be easily adapted to the desired application, the electronic components that conform it must be easily modified. Nowadays, this is achieved by using circuits based in reprogrammable logic, as the FPGAs.

A FPGA by itself can be regarded as a box full of flip-flops, logic gates and RAM, that can be interconnected in a certain way, according to the preferences of the user, by a simple programming method.

The design that is programmed into the FPGA must implement the new function being added to the PC, and must also be capable of communicating with the PC through the PCI bus.

Given the complexity of the PCI bus, the design can be split in two modules, one in charge of communicating through the PCI bus, and the other responsible for providing the new function.

The module that takes care of the communication is usually called PCI core, and simplifies the use of the PCI bus by hiding the specific details (error checking, address decoding, signaling, etc.).

Initially the project consisted of developing a PCI core and a generic device driver for it, both under an open source kind of license,

The first versions of the PCI core were tested with an existing configurable board belonging to the IIE (Instituto de Ingeniería Eléctrica). The first tests showed the constraints in performance imposed by the FPGA chips used in those boards. Because of this, the development and manufacturing of a low cost PCI card based on FPGA devices, became part of the objectives of the project.

The final result is a hardware development platform for devices using the PCI bus.

The platform contains:

GRACIAS!