La utilización de un PC para desarrollar e implementar aplicaciones hardware es una alternativa interesante, debido a, su gran difusión y bajo costo, el tener resuelta la comunicación con el mundo exterior (con personas y máquinas), la existencia de infinidad de herramientas de desarrollo y prueba.

El PC, siendo un sistema de propósito general, puede ser ajustado a las necesidades del usuario agregando placas con la electrónica necesaria, acompañadas de software que permita controlarlas. Un posible ejemplo es el procesamiento de imágenes de video: basta colocar una tarjeta adquisidora de video y configurar su software controlador para hacer que una aplicación de procesamiento de imágenes, ejecutándose en el PC, pueda procesar las imágenes adquiridas con la placa.

Hace algunos años el bus ISA era el estándar para desarrollar placas que se conectaran a un PC, lo cual era relativamente sencillo.

A mediados de los 90, las exigencias crecientes en cuanto a velocidad de transferencias de datos superaron la capacidad del bus ISA. Esto motivó que surgieran varias tecnologías de transición que derivaron en la aparición de un nuevo estándar: el bus PCI [10.1.I ].

El bus PCI presenta varias ventajas con respecto al bus ISA, como ser su independencia de la arquitectura del procesador, su tasa de transferencia más elevada y la implementación de control de errores en las transferencias.

Es interesante entonces poder hacer uso del bus PCI de un PC para desarrollar aplicaciones de todo tipo.

Si a esto agregamos que una misma placa pueda reconfigurarse y servir para resolver diferentes problemas, la alternativa se vuelve aún más atractiva.

Cuando mencionamos la posibilidad de reconfiguración de una placa nos estamos refiriendo a utilizar circuitos integrados cuya lógica sea configurable por el usuario (FPGAs, PLDs, etc.)

Pero, como su nombre lo recuerda, la lógica configurable debe ser configurada.

Un FPGA sin configurar es como una caja llena de flip-flops, compuertas lógicas y memorias RAM. Es necesario interconectarlos de una cierta manera, siguiendo un cierto diseño, para que realicen una función útil.

Por lo tanto, para que una placa con un FPGA permita agregar ciertas funcionalidades a un PC, se debe especificar, en algún lenguaje de descripción de circuitos, un diseño que implemente estas funcionalidades y, a la vez, haga uso del bus PCI para comunicarse.

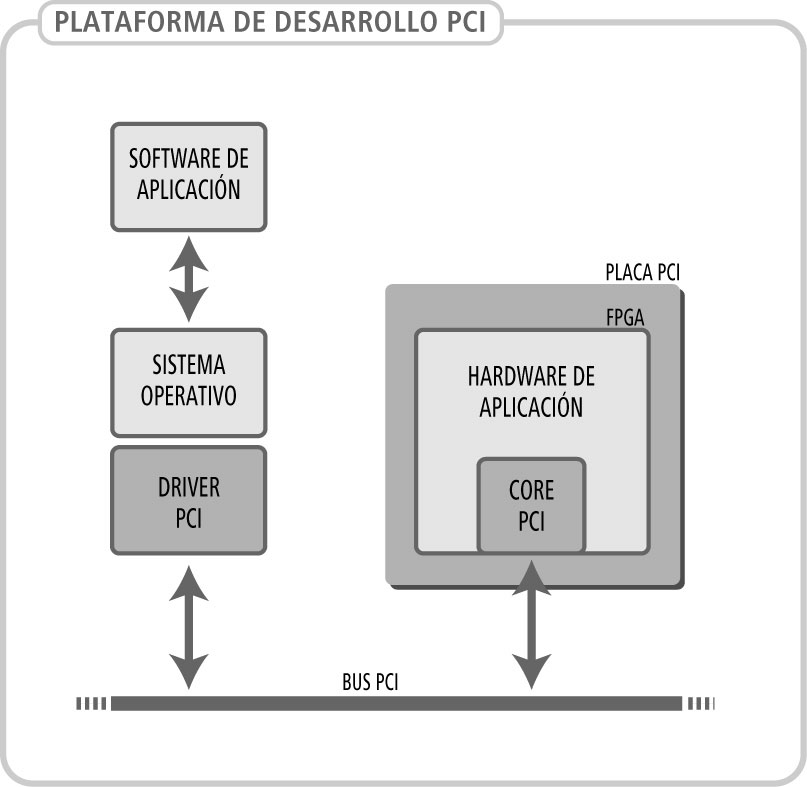

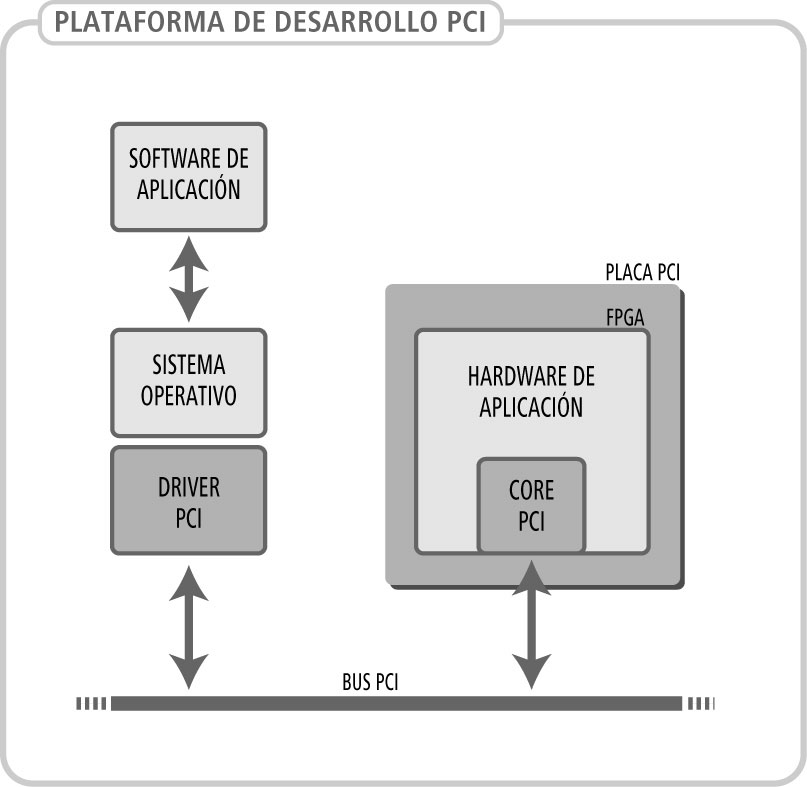

Dada la complejidad del bus PCI, este diseño podría separarse en dos bloques, uno que resuelva la comunicación con el bus PCI y otro que implemente la funcionalidad.

El bloque que resuelve la comunicación es llamado core PCI y se encarga de encapsular los detalles del estándar (manejo de errores, decodificación de direcciones, señalizaciones, etc.).

Existen cores PCI de varios fabricantes pero, al ser todos comerciales, su utilización requiere de la compra de una licencia. El IIE cuenta con la licencia de un core PCI donada por la compañía ALTERA, cuyo costo es de U$S 8,995.

Al momento de comenzar el proyecto no se encontró ningún core PCI de libre distribución. Fue esta una de las motivaciones principales para realizar el proyecto.

En resumen:

El bus PCI está disponible en todas las PCs hoy en día.

Por otro lado, las placas de lógica reconfigurable son muy útiles para el desarrollo de prototipos, ya sea para enseñanza o investigación, o para la producción en pequeñas cantidades o de corta vida.

Resulta entonces más que razonable la combinación PC y placa con lógica reconfigurable, y su nexo es el bus PCI.

Para poder desarrollar una aplicación que, en forma sencilla, haga uso de los recursos del bus, debe de utilizarse algún bloque que encapsule los detalles.

Este proyecto plantea desarrollar este bloque y difundirlo bajo una licencia de libre distribución.

Se comenzó por el diseño del core PCI para configurar el FPGA de la placa ARC-PCI y al completar un diseño que no tenia aún todas las funcionalidades implementadas, se comprobó que al sintetizarlo para los FPGAs de la placa ARC-PCI no cumplía con los requerimientos de performance necesarios.

El problema es que el FPGA de la ARC-PCI (EPF1K50RC240-3) es un chip lento para el tipo de diseño a implementar. Incluso el core PCI desarrollado por ALTERA con una aplicación simple debe ser sintetizado poniendo especial cuidado en las opciones de síntesis elegidas, dado que de otra forma no se llega a la performance requerida.

Ante este problema se estudiaron dos posibles soluciones, comprar una nueva placa de desarrollo o diseñar una.

Al momento de tomar la decisión no se encontraron placas de bajo costo, por ello se optó por realizar y fabricar un diseño propio.

Otras motivaciones fueron: recabar experiencia práctica en la fabricación de placas PCI, diseño de placas multicapa para frecuencias del orden de decenas de MHz, y uso de componentes de soldadura superficial.

Un esquema de la plataforma completa se muestra a continuación: