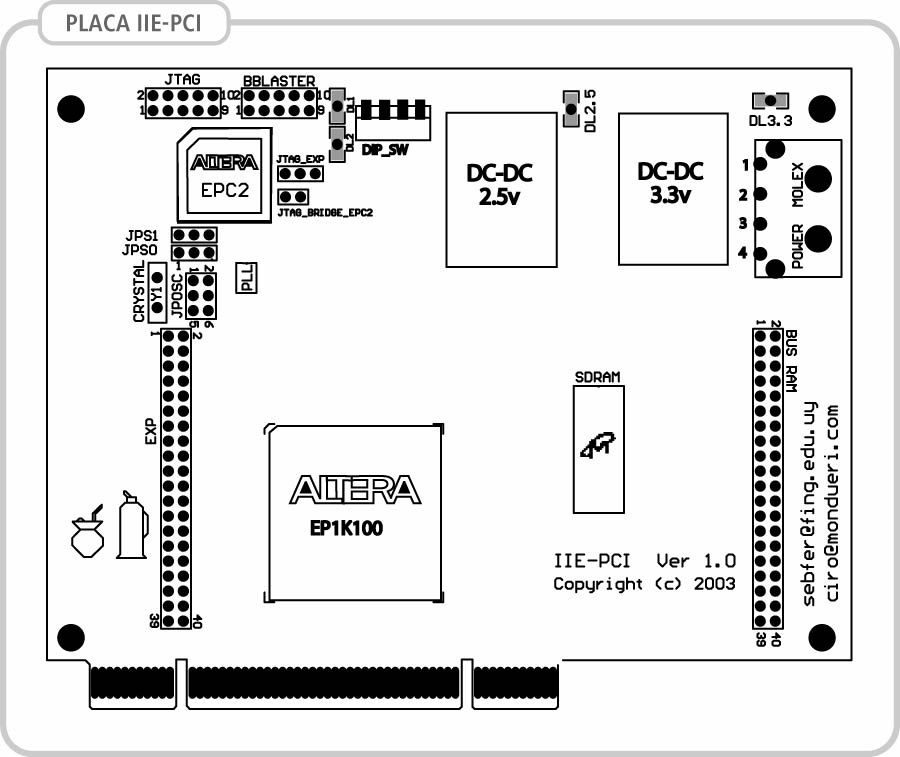

El corazón de la placa es un FPGA de ALTERA, en el cual se implementa toda la lógica de la placa. Las patas de propósito general están conectadas al bus PCI, a la memoria SDRAM y a conectores de expansión.

El FPGA se desconfigura al quitarle la alimentación, por lo cual la placa cuenta con una EPROM de configuración que permite que el FPGA se autoconfigure al encenderse.

Tanto la programación de la EPROM como la configuración del FPGA se realizan mediante el protocolo JTAG.

Cuenta con conectores del tipo header hembra que permiten conectar placas de expansión al FPGA haciendo a la vez de soporte.

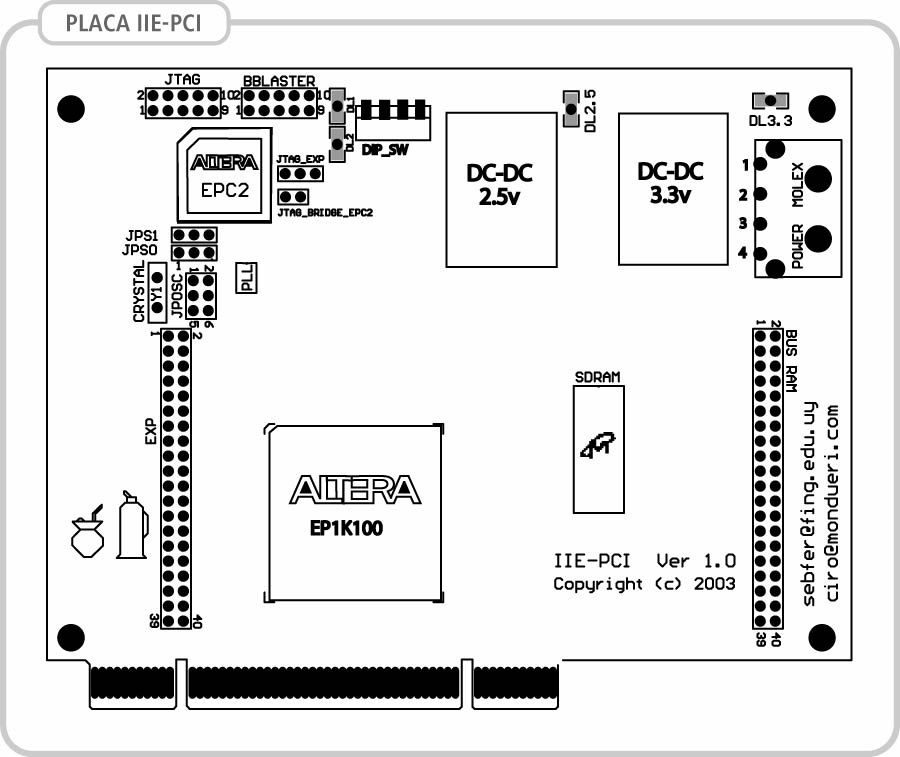

Un PLL en la placa provee señal de reloj al FPGA, la memoria y uno de los conectores de expansión. Estas señales de reloj pueden ser múltiplos de la frecuencia del reloj PCI o de la frecuencia de un cristal; esto se selecciona mediante jumpers en la placa.

La alimentación de los componentes proviene de dos conversores DC-DC, uno a 3.3V y el otro a 2.5V. La distribución de la alimentación (VCC y tierra) se hace utilizando las 2 capas interiores de las 4 que componen la placa.

El plano de tierra esta conectado a los contactos de GND del bus PCI y a los pines centrales del conector Molex.

La placa esta diseñada para ser alimentada desde el bus PCI o utilizando una fuente de PC. Cuando la placa esta conectada al bus PCI no es necesario proveer de alimentación adicional en el conector Molex.

Los expansores tiene disponibles fuentes y tierras en sus pines:

EL PLL genera una señal de reloj por el pin Q/N y múltiplos de esta por los pins Q[2..0]. La frecuencia de Q/N esta dada por un cristal o el reloj PCI.

Las señales se conectan de la siguiente forma:

Observación: la señal de reloj que llega a la SDRAM, puede provenir de Q1 o del pin 176 del FPGA, que se comparte con la señal IO_EXP30 (pin 6 del conector EXP). Esto se selecciona soldando una resistencia de 0 ohm en una de dos posibles posiciones. Esto fue hecho para poder generar la señal de reloj desde dentro del FPGA.

| Fuente | 1-2 | 3-4 | 5-6 |

|---|---|---|---|

| Cristal | Open | Closed | Closed |

| PCI | Closed | Open | Open |

| Factor | JPS1 | JPS0 |

|---|---|---|

| No Especificado | 2-3 | 2-3 |

| x2 | 2-3 | -- |

| x3 | 2-3 | 1-2 |

| x4 | -- | 2-3 |

| x5 | -- | -- |

| x6 | -- | 1-2 |

| x7 | 1-2 | 2-3 |

| x8 | 1-2 | -- |

| TEST (CLKIN bypass VCO) | 1-2 | 1-2 |

En la tabla se indica la posición del jumper, cuando se indica -- debe dejarse al aire los contactos.

La frecuencia del reloj de entrada o del cristal y el factor de multiplicación deben cumplir la siguiente inecuación: 25/N < CLKIN < 160/N

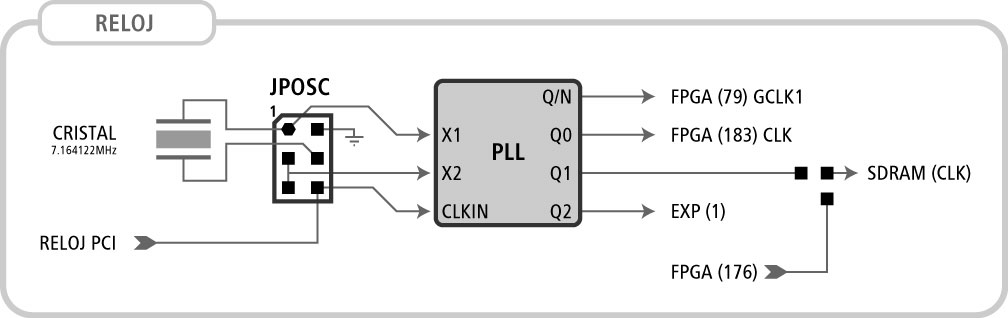

La placa permite encadenar la EPC2, el FPGA y cualquier otro dispositivo conectado al expansor que soporte el protocolo. El orden de los dispositivos en la cadena JTAG es el siguiente:

La cadena entre los pines TDI y TDO del HEADER JTAG siempre debe de estar cerrada. En caso de que la EPC2 no esté presente o que no haya un dispositivo que soporte el protocolo JTAG en el conector de expansión, se deben manipular los jumpers JTAG_EXP y JTAG_BRIDGE_EPC2 para que la cadena JTAG quede cerrada de todas formas.

| EPC2 | JTAG_BRIDGE_EPC2 |

|---|---|

| presente | open |

| ausente | closed |

| expansor | JTAG_EXP |

|---|---|

| utilizado | 1-2 |

| libre | 2-3 |

La EPC2 esta conectada a los mismos pines del FPGA que el conector BBLASTER, por lo cual cuando se conecte el ByteBlasterMV la EPC2 no debe estar presente.

Tanto el EP1K100 como la EPC2 funcionan a 3.3V pero soportan voltajes de 5V en sus pines, esto hace posible utilizar un ByteBlaster estándar (alimentación 5V) en lugar del ByteBlaterMV. Para ello debe de conectarse el pin 4 del programador a 5V en lugar de al conector de la placa (provee 3.3V).

5V están disponibles en el pin 5 del conector EXP.

Al conector EXP llegan los pines libres del FPGA, fuentes de 3.3V y 5V y GND.

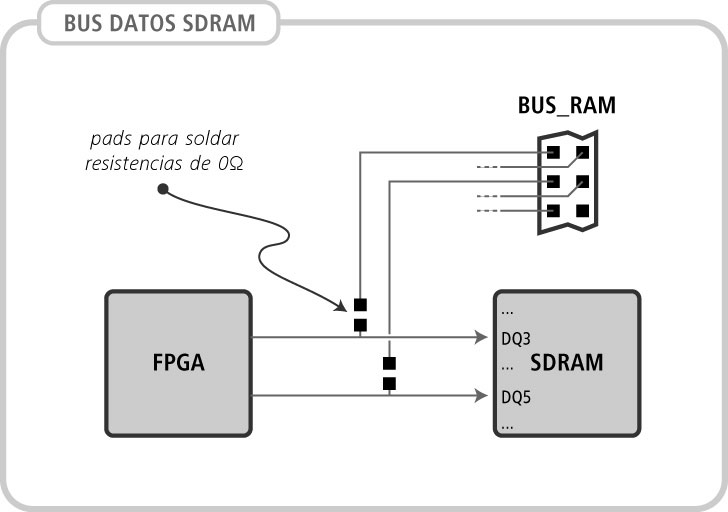

En el expansor del bus RAM pueden verse las señales del bus de datos de la SDRAM si se sueldan las resistencias de 0 ohm correspondientes.

Esto ultimo permite hacer aplicaciones que lean datos de la SDRAM o utilizar estos pines sin usar la RAM. Para ello se debe de desactivar la SDRAM mediante la pata CS que esta conectada al pin 175 del FPGA.

Señales en bus EXP (tabla dispuesta con la forma del expansor):

| PIN_EXP | SEÑAL(PIN FPGA) | - | SEÑAL(PIN FPGA) | PIN_EXP |

|---|---|---|---|---|

| 1 | EXPCLK | [] | GND | 2 |

| 3 | GND | [] | 3.3v | 4 |

| 5 | 5V | [] | IO_EXP30(176) | 6 |

| 7 | IO_EXP29(197) | [] | IO_EXP28(198) | 8 |

| 9 | IO_EXP27(199) | [] | IO_EXP26(200) | 10 |

| 11 | IO_EXP25(202) | [] | IO_EXP24(203) | 12 |

| 13 | IO_EXP23(204) | [] | IO_EXP22(205) | 14 |

| 15 | IO_EXP21(206) | [] | IO_EXP20(207) | 16 |

| 17 | IO_EXP19(208) | [] | IO_EXP18(7) | 18 |

| 19 | IO_EXP17(8) | [] | IO_EXP16(9) | 20 |

| 21 | IO_EXP15(10) | [] | IO_EXP14(11) | 22 |

| 23 | IO_EXP13(12) | [] | IO_EXP12(13) | 24 |

| 25 | IO_EXP11(14) | [] | IO_EXP10(15) | 26 |

| 27 | IO_EXP9(16) | [] | IO_EXP8(17) | 28 |

| 29 | IO_EXP7(18) | [] | IO_EXP6(24) | 30 |

| 31 | IO_EXP5(25) | [] | IO_EXP4(26) | 32 |

| 33 | IO_EXP3(27) | [] | IO_EXP2(28) | 34 |

| 35 | IO_EXP1(29) | [] | IO_EXP0(30) | 36 |

| 37 | JTAG_EXP_TDI | [] | JTAG_EXP_TDO | 38 |

| 39 | FPGA_TMS | [] | JTAG_TCK | 40 |

Señales del bus RAM (tabla dispuesta con la forma del expansor):

| PIN_RAM | SEÑAL | - | SEÑAL | PIN_RAM |

|---|---|---|---|---|

| 1 | GND | [] | DQ 0 | 2 |

| 3 | DQ 1 | [] | DQ 2 | 4 |

| 5 | DQ 3 | [] | DQ 4 | 6 |

| 7 | DQ 5 | [] | DQ 6 | 8 |

| 9 | DQ 7 | [] | GND | 10 |

| 11 | GND | [] | DQ 15 | 12 |

| 13 | DQ 14 | [] | DQ 13 | 14 |

| 15 | DQ 12 | [] | DQ 11 | 16 |

| 17 | DQ 10 | [] | DQ 9 | 18 |

| 19 | DQ 8 | [] | GND | 20 |

| 21 | GND | [] | DQ 31 | 22 |

| 23 | DQ 30 | [] | DQ 29 | 24 |

| 25 | DQ 28 | [] | DQ 27 | 26 |

| 27 | DQ 26 | [] | DQ 25 | 28 |

| 29 | DQ 24 | [] | GND | 30 |

| 31 | GND | [] | DQ 16 | 32 |

| 33 | DQ 17 | [] | DQ 18 | 34 |

| 35 | DQ 19 | [] | DQ 20 | 36 |

| 37 | DQ 21 | [] | DQ 22 | 38 |

| 39 | DQ 23 | [] | GND | 40 |

DQ NN indica que la señal de datos NN de la SDRAM esta conectado a pin del expansor.

La siguiente tabla indica las conexiones entre el FPGA y la memoria.

Bus de Datos

| SDRAM | Pin FPGA | - | SDRAM | Pin FPGA |

|---|---|---|---|---|

| DQ0 | 196 | DQ16 | 126 | |

| DQ1 | 195 | DQ17 | 125 | |

| DQ2 | 193 | DQ18 | 122 | |

| DQ3 | 192 | DQ19 | 121 | |

| DQ4 | 191 | DQ20 | 120 | |

| DQ5 | 190 | DQ21 | 119 | |

| DQ6 | 189 | DQ22 | 116 | |

| DQ7 | 187 | DQ23 | 115 | |

| DQ8 | 164 | DQ24 | 136 | |

| DQ9 | 166 | DQ25 | 139 | |

| DQ10 | 167 | DQ26 | 140 | |

| DQ11 | 168 | DQ27 | 141 | |

| DQ12 | 169 | DQ28 | 142 | |

| DQ13 | 170 | DQ29 | 143 | |

| DQ14 | 172 | DQ30 | 144 | |

| DQ15 | 173 | DQ31 | 147 |

Bus de Direcciones

| Sdram | Pin FPGA |

|---|---|

| A0 | 132 |

| A1 | 131 |

| A2 | 128 |

| A3 | 149 |

| A4 | 150 |

| A5 | 157 |

| A6 | 158 |

| A7 | 159 |

| A8 | 160 |

| A9 | 161 |

| A10 | 133 |

| A11 | 174 |

| BA0 | 135 |

| BA1 | 134 |

| DQM0 | 186 |

| DQM1 | 163 |

| DQM2 | 127 |

| DQM3 | 148 |

Señales de control

| Sdram | Pin FPGA |

|---|---|

| R\A\S\ | 177 |

| C\A\S\ | 179 |

| C\S\0\ | 175 |

| CKE | 162 |

| W\E\ | 180 |

La siguiente tabla indica las conexiones entre el FPGA y el conector PCI.

Bus de datos y direcciones

| PCI | Pin FPGA | - | PCI | Pin FPGA |

|---|---|---|---|---|

| AD0 | 114 | AD16 | 69 | |

| AD1 | 113 | AD17 | 68 | |

| AD2 | 112 | AD18 | 67 | |

| AD3 | 111 | AD19 | 65 | |

| AD4 | 104 | AD20 | 64 | |

| AD5 | 103 | AD21 | 63 | |

| AD6 | 102 | AD22 | 61 | |

| AD7 | 101 | AD23 | 60 | |

| AD8 | 99 | AD24 | 56 | |

| AD9 | 97 | AD25 | 55 | |

| AD10 | 96 | AD26 | 54 | |

| AD11 | 95 | AD27 | 53 | |

| AD12 | 94 | AD28 | 47 | |

| AD13 | 93 | AD29 | 46 | |

| AD14 | 92 | AD30 | 45 | |

| AD15 | 90 | AD31 | 44 |

Bus de comandos

| PCI | Pin FPGA |

|---|---|

| CNBE0 | 100 |

| CNBE1 | 89 |

| CNBE2 | 70 |

| CNBE3 | 57 |

Señalización de transacciones

| PCI | Pin FPGA |

|---|---|

| IDSEL | 58 |

| F\R\A\M\E\ | 71 |

| I\R\D\Y\ | 73 |

| T\R\D\Y\ | 74 |

| D\E\V\S\E\ | 75 |

Arbitraje de bus

| PCI | Pin FPGA |

|---|---|

| L\O\C\K\ | 85 |

| G\N\T\ | 40 |

| R\E\Q\ | 41 |

| R\S\T\ | 39 |

| S\T\O\P\ | 83 |

Interrupciones

| PCI | Pin FPGA |

|---|---|

| I\N\T\A\ | 31 |

| I\N\T\B\ | 36 |

| I\N\T\C\ | 37 |

| I\N\T\D\ | 38 |

Reporte de errores

| PCI | Pin FPGA |

|---|---|

| S\E\R\R\ | 87 |

| P\E\R\R\ | 86 |

| PAR | 88 |

Las 4 llaves de dos posiciones están conectadas, utilizando pull-ups, a 4 patas de entrada del FPGA.

Cuando están abiertas (arriba) se tiene un 1 lógico y cuanto están cerradas (abajo) se tiene un 0 lógico.

CLOCK_LOCK: LED1 (led azul) esta conectado a CLOCK_LOCK. En el compilador se puede escoger que se encienda si el PLL interno del FPGA se "engancha" con la señal de reloj. En caso de no utilizarse esta funcionalidad puede ser manejado por una aplicación.

INIT_DONE: Si el FPGA se configura correctamente, se enciende LED2 (led verde). También puede ser manejado por una aplicación luego de la configuración del FPGA.

| Componente | PIN FPGA |

|---|---|

| LED 1 (Azul, activo nivel alto) | 62 |

| LED 2 (Verde, activo nivel bajo) | 19 |

| SW_DIP 4 | 78 |

| SW_DIP 3 | 184 |

| SW_DIP 2 | 80 |

| SW_DIP 1 | 182 |

En el sitio web de Altera (www.altera.com) se encuentran disponibles versiones gratuitas del Max+Plus II y del Quartus II:

A continuación se describen los procedimientos para:

ADVERTENCIA: Si se desea programar la placa colocada en el bus PCI de un PC y programarla desde otro PC, se debe tener especial cuidado con las diferencia de potencial entre las tierras. Se recomienda retirar la placa del bus PCI, programar la EPC2 y luego volverla a conectar al bus PCI.

Ajustes en la placa

Para programar la EPC2, deben ajustarse los jumpers JTAG_EXP y JTAG_BRIDGE_EPC2 de forma que la cadena JTAG este cerrada.

JTAG_BRIDGE_EPC2 debe dejarse abierto

El jumper de JTAG_EXP debe de colocarse en alguna de las posiciones indicadas en la tabla dependiendo de si el expansor esta libre o esta siendo utilizado por una placa que soporta el protocolo JTAG.

| expansor | JTAG_EXP |

|---|---|

| utilizado | 1-2 |

| libre | 2-3 |

Conexión de ByteBlasterMV

El ByteBlasterMV debe ser conectado al puerto paralelo del PC y al conector JTAG de la placa.

Debe coincidir el pin 1 del conector con el pin 1 del ByteBlasterMV (lado rojo del cable).

Por más información referirse a la hoja de datos del ByteBlasterMV.

Ajustes en MAX+PLUS II

Ajustes en la placa

Para programar el EP1K100, deben manipularse los jumpers JTAG_EXP y JTAG_BRIDGE_EPC2 de forma que la cadena JTAG este cerrada.

El jumper JTAG_BRIDGE_EPC2 no debe ser colocado pues se cortocircuitarían las patas TSI y TDO de la EPC2.

El jumper de JTAG_EXP debe de colocarse en alguna de las posiciones indicadas en la tabla dependiendo de si el expansor esta libre o esta siendo utilizado por una placa que soporta el protocolo JTAG.

| expansor | JTAG_EXP |

|---|---|

| utilizado | 1-2 |

| libre | 2-3 |

Conexión de ByteBlasterMV

El ByteBlasterMV debe ser conectado al puerto paralelo del PC y al conector JTAG de la placa.

Debe coincidir el pin 1 del conector con el pin 1 del ByteBlasterMV (lado rojo del cable).

Por más información referirse a la hoja de datos del ByteBlasterMV.

Ajustes en MAX+PLUS II

Ajustes en la placa

Para programar el EP1K100, deben manipularse los jumpers JTAG_EXP y JTAG_BRIDGE_EPC2 de forma que la cadena JTAG este cerrada.

El jumper JTAG_BRIDGE_EPC2 debe ser colocado para cerrar la cadena JTAG.

El jumper de JTAG_EXP debe de colocarse en alguna de las posiciones indicadas en la tabla dependiendo de si el expansor esta libre o esta siendo utilizado por una placa que soporta el protocolo JTAG.

| expansor | JTAG_EXP |

|---|---|

| utilizado | 1-2 |

| libre | 2-3 |

Conexión de ByteBlasterMV

El ByteBlasterMV debe ser conectado al puerto paralelo del PC y al conector JTAG de la placa.

Debe coincidir el pin 1 del conector con el pin 1 del ByteBlasterMV (lado rojo del cable).

Por más información referirse a la hoja de datos del ByteBlasterMV.

Ajustes en MAX+PLUS II

Ajustes en la placa

Para configurar el EP1K100 utilizando el modo serie de programación (ByteBlasterMV en conector BBLASTER), la EPC2 no debe estar presente. La EPC2 utiliza este modo para configurar el EP1K100, por lo que sus patas están también unidas al conector BBLASTER.

Ajustes en la placa

La EPC2 debe ser retirada de su zócalo.

Conexión de ByteBlasterMV

El ByteBlasterMV debe ser conectado al puerto paralelo del PC y al conector BBLASTER de la placa.

Debe coincidir el pin 1 del conector con el pin 1 del ByteBlasterMV (lado rojo del cable).

Por más información referirse a la hoja de datos del ByteBlasterMV.

Ajustes en MAX+PLUS II

Ajustes en la placa

JTAG_BRIDGE_EPC2 no debe tener colocado el Jumper

El jumper de JTAG_EXP debe de colocarse en alguna de las posiciones indicadas en la tabla dependiendo de si el expansor esta libre o esta siendo utilizado por una placa que soporta el protocolo JTAG.

| expansor | JTAG_EXP |

|---|---|

| utilizado | 1-2 |

| libre | 2-3 |

Conexión de ByteBlasterMV

El ByteBlasterMV debe ser conectado al puerto paralelo del PC y al conector JTAG de la placa.

Debe coincidir el pin 1 del conector con el pin 1 del ByteBlasterMV (lado rojo del cable).

Por más información referirse a la hoja de datos del ByteBlasterMV.

Ajustes en MAX+PLUS II