El proyecto consistió en desarrollar una placa PCI basada en lógica programable para ser utilizada como plataforma de desarrollo.

Se desarrollaron además herramientas que facilitan el diseño de aplicaciones, entre las más importantes se encuentran un core PCI sintetizable y un driver para Linux que permite comunicarse con la placa.

El bus PCI es el estándar actual para la conexión de tarjetas en un PC. Permite conectar placas que le agregan funcionalidades, por ejemplo placas de sonido, capturadoras de video, placas de red, co-procesadores matemáticos, etc. Estas tarjetas suelen llamarse placas PCI.

El diseño de prototipos de placas PCI, ya sea para su posterior uso comercial o para investigación, se ve acelerado si se comienza el desarrollo a partir de un placa de propósito general, ya existente, que pueda ser rápidamente adaptada según las necesidades del diseño.

Haciendo énfasis en la adaptabilidad de la placa a la aplicación a desarrollar, la electrónica que la conforme debe ser fácilmente modificable. Hoy día, este objetivo se logra utilizando circuitos integrados de lógica reconfigurable, como ser los FPGA. Un FPGA puede verse como una caja llena de flip-flops, compuertas lógicas y memorias RAM, que pueden ser interconectados de una cierta manera, a gusto del usuario, al configurarlo.

Partiendo de una placa PCI cuyo corazón sea un FPGA, el diseño de un prototipo consistirá básicamente en realizar, en algún lenguaje de descripción de circuitos, un diseño que configure el FPGA para que se comporte según los requerimientos establecidos. Como un FPGA puede reconfigurarse, en caso de detectar un error en el funcionamiento, basta corregir el error y volver a configurar el FPGA.

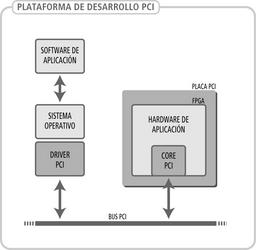

El diseño a programar en el FPGA debe implementar la funcionalidad que se desea agregar al PC y debe comunicarse utilizando el bus PCI. Dada la complejidad del bus PCI, este diseño podría separarse en dos bloques, uno que resuelva la comunicación con el bus y otro que implemente la funcionalidad. El bloque que resuelve la comunicación es llamado core PCI y se encarga de encapsular los detalles del estándar (manejo de errores, decodificación de direcciones, señalizaciones, etc.).

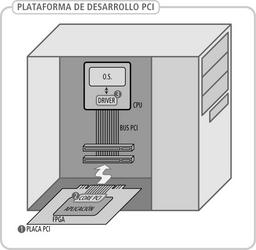

El resultado final del proyecto es una plataforma de desarrollo para diseños hardware que utilizan el bus PCI.

Componen la plataforma:

- placa de propósito general con un conector para bus PCI y lógica reconfigurable.

- diseño modular (core PCI) que encapsula los detalles de funcionamiento del bus PCI, para ser utilizado por la aplicación que se configura en el FPGA.

- software controlador (driver) que permite que desde programas ejecutándose en un PC se pueda acceder a la placa.

Bloques que integran el proyecto: